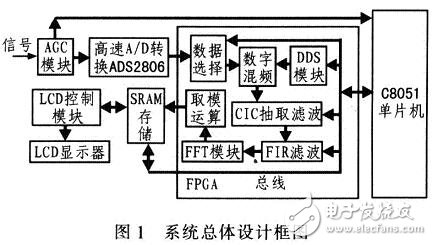

設計方案

圖1為系統設計總體框圖。該系統采用C8051($8.5125)系列單片機中的 C8051($8.5125)F121作為控制器,CvcloneⅢ系列EP3C40F484C8($86.5000)型FPGA為數字信號算法處理單元。系統設計遵循抽樣定理,在時域內截取一段適當長度信號,對其信號抽樣量化,按照具體的步驟求取信號的頻譜,并在LCD上顯示信號的頻譜,同時提供友好的人機會話功能。該系統zui小分辨率為1 Hz,可分析帶寬為0~5 MHz的各種信號。

由于單片機C8051($8.5125) F121內部集成A/D轉換器,能夠有效測量自動增益控制AGC壓差,計算出對輸入信號的放大倍數;另外,該單片機內置高速控制內核和豐富的存儲器,使其能夠控制整個系統;EP3C40F484C8($86.5000)型FPGA內置豐富的存儲器資源,確保該系統具有足夠的空間存儲采集的點數,完成離散傅里葉變換、數字濾波器、數字混頻等信號處理。

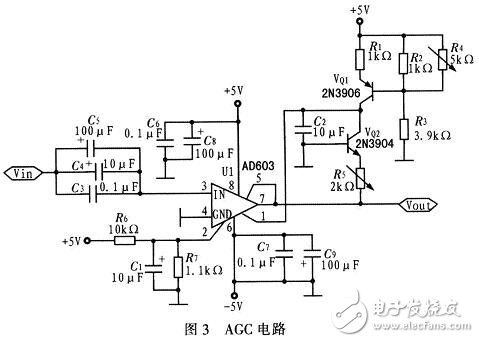

AGC電路

輸入信號經高速A/D采樣,信號幅度必須滿足A/D的采樣范圍,zui高為2-3V,因此該系統設計應加AGC電路。AGC電路采用AD603($6.4440)型線性增益放大器。圖3為AGC電路。

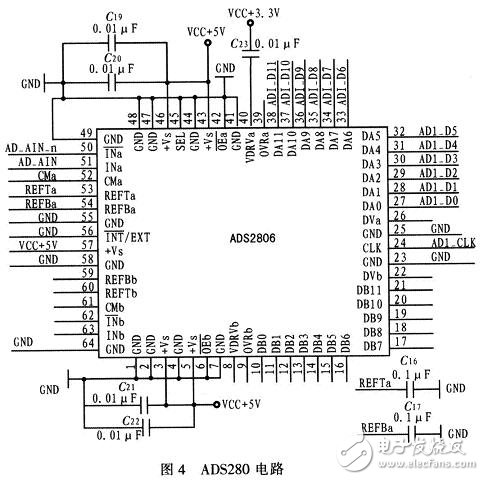

A/D轉換電路

ADS2806($21.5437)是一款12位A/D轉換器,其特點為:無雜散信號動態范圍(SFDR)為73 dB;信噪比(SNR)為66 dB;具有內部和外部參考時鐘;采樣速率為32 MS/s。圖4為ADS2806($21.5437)的電路。為使A/D轉換更穩定,在A/D轉換器的電源引腳上增加濾波電容,抑制電源噪聲。該電路結構簡單,在時鐘CLK的驅動下,數據端口實時輸出數據,供FPGA讀取。

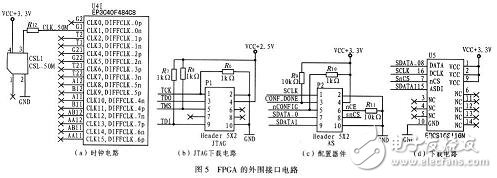

FPGA及外圍接口模塊

選用Cyclone($898.9000)Ⅲ系列 EP3C40F484($86.5000)型FPGA,該器件內部有39 600個LE資源,有1 134 000 bit的存儲器,同時還有126個乘法器和4個PLL鎖相環。由于該器件內部有大量資源,因而可滿足其內部實現數字混頻、數字濾波、以及FFT運算。FP -GA正常工作時,主要需要的外部接口有:時鐘電路、JTAG下載電路、配置器件及下載電路。圖5為FPGA的外圍接口電路。

該系統能夠方便地在LCD上顯示信號的頻譜結構圖。操作簡單,非常適合教學實驗室學生使用。

文章來源:電子發燒友